DOA bus

From PHCC

Contents

Digital Out Type A (DOA) Bus

Electrical Layer Interface

This is a unidirectional multidrop bus. Data flows only in one direction: from the PHCC motherboard to the DOA daughterboards, all connected daughterboards see the data at the same time. It is a synchronous two wire bus, one data and one clock line.

Transmission Layer Interface

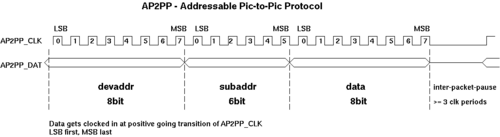

Each daughterboard has a 8bit long address, this means that with the current implementation, up to 256 daughterboards could theoretically be connected to DOA. Repeaters/signal conditioners should be used with longer cables and for every few daughterboards. The protocol is called AP2PP, Addressable PIC to PIC Protocol. AP2PP code for the receiving side (daugherboards) is available for several different PIC microcontrollers. The code and protocol is very simple. Bits are serially transmitted, LSB first. Data gets latched in at the positive (low-to-high) going transition of the clk.

The current clock speed on the DOA bus is TBD.

Diagram

Here's a diagram that shows the communication between the Motherboard to the DOA-type daughterboards.

Just for clarification: DOA (Digitial Out Type A) is the name of the bus, and AP2PP (Adressable Pic-to-Pic Protocol) is the name of the protocol that specifies how data is transferred on that bus.

Remember, the DOA bus has two data wires plus power (+5V DC, GND). The data lines are called DOA_CLK (sometimes referred to as AP2PP_CLK) and DOA_DATA (sometimes referred to as AP2PP_DAT).

Data is transferred on via AP2PP as "packets". A "packet" has three "fields": 1. the 8bit device address field (devaddr) 2. the 6bit sub address field (subaddr) 3. the 8bit payload data field (data)

Each DOA board has a unique devaddr. This theoretically allows 256 DOA daughterboards to be addressed. Without signal amplifiers, connecting that many daughterboards to the bus will get you into trouble of course.

The meaning of the subaddr is dependant on what daughterboard and firmware revision you are talking to.